RING COUNTER

Register geser ring counter adalah rangkaian register geser yang dilengkapi dengan jaringan loop tertutup antara output Q flip-flop terakhir ke input pada flip-flop pertama. Jaringan loop tertutup pada register geser ini mengakibatkan terjadinya pergeseran data secara berurutan setiap pulsa clock diberikan secara terus menerus karena terjadi looping data. Kondisi seperti ini disebut sebagai keadaan “recirculates” sehingga register geser yang memiliki kondisi seperti ini disebut sebagai register geser ring counter. Rangkaian dasar ring counter dapat dilihat pada gambar berikut.

Rangkaian Dasar Register Geser Ring Counter 4 Bit

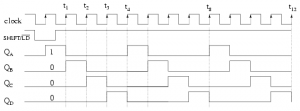

Rangkaian register geser ring counter adalah register geser yang dilengkapi dengan jaringan umpan-balik dari data output terakhir ke jalur input flip-flop pertama. Rangkaian register geser ring counter diatas adalah register geser 4 bit yang disusun dari D-FF sehingga membentuk register geser ring counter 4 bit. Register geser ring counter dibuat denga data flip-flop (D-FF). Output dari rangkaian register geser ring counter diatas dapat digambarkan dalam timing diagram sebagai berikut.

Timing Diagram Register Geser Ring Counter 4 Bit

Dari timing diagram diatas terlihat bahawa data yang diberikan ke rangkain register geser ring counter tersebut digeser ke posisi MSB kemudian umpankan kembali ke jalur input flip-flop pertama. Register geser ring counter ini sering digunakan atau diaplikasikan pada rangkaian kontrol kecepatan motor steper, rangkaian lampu berjalan dan rangkaian sequensial yang lain.